B10H0710N40D

Download datasheetB10H0710N40D

Download datasheetLDMOS 2-stage integrated Doherty MMIC

The B10H0710N40D is a dual section 2-stage fully integrated Doherty MMIC solution using Ampleon's state of the art 50 V LDMOS technology. The carrier and peaking device, input splitter, output combiner and pre-match are integrated in each section. This multiband device is perfectly suited as general purpose driver in the frequency range 700 MHz to 1 GHz. Available in LGA outline.

Features and benefits

- Integrated input splitter

- Integrated output combiner

- Source impedance 50 Ω

- Pre-matched output

- No output circulator needed thanks to quad-combined configuration

- High linearity

- Designed for large RF and instantaneous bandwidth operation

- Independent control of carrier and peaking bias

- Integrated ESD protection

- High power gain

- For RoHS compliance see the product details on the Ampleon website

Applications

- 4G/5G macrocell base station driver

- 4G/5G microcell base station

Parametrics

| Symbol | Parameter | Conditions | Min | Typ/Nom | Max | Unit |

|---|---|---|---|---|---|---|

| frange | frequency range | 700 | 1000 | MHz | ||

| PL(1dB) | nominal output power at 1 dB gain compression | 50 | W | |||

| Test signal: Pulsed CW | ||||||

| VDS | drain-source voltage | [0] | 48 | V | ||

| Gp | power gain | PL = 2.51 W (34 dBm) [0] | 27 | 31 | 35 | dB |

| ηD | drain efficiency | PL = 2.51 W (34 dBm) [0] | 20 | 25 | % | |

| RLin | input return loss | PL = 2.51 W (34 dBm) [0] | -20 | -10 | dB | |

| ηD | drain efficiency | PL = PL(1db) [0] | 50 | 54 | % | |

Package / Packing

| Type number |

Package type, (Package outline) |

Outline version | Packing | Product status | Marking |

Orderable part number, (Ordering code (12NC)) |

|---|---|---|---|---|---|---|

| B10H0710N40D | LGA-12x8 (LGA-12x8-34-2) |

lga-12x8-34-2_po | TR13; 3000-fold; 24 mm; dry pack | Active | Standard Marking |

B10H0710N40DX (9349 606 85525) |

| TR7; 500-fold; 24 mm; dry pack | Active | Standard Marking |

B10H0710N40DYZ (9349 606 85535) |

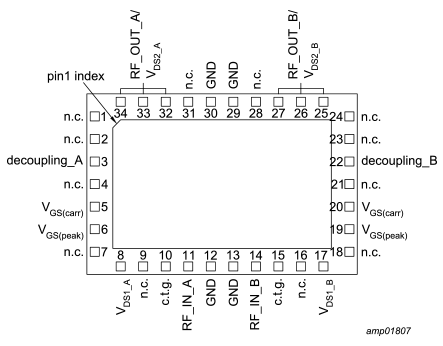

Pinning info

| Pin | Symbol | Description | Simplified outline | Graphic symbol |

|---|---|---|---|---|

| 1 | n.c | not connected |

|

|

| 2 | n.c. | not connected | ||

| 3 | decoupling_A | video-lead for decoupling of section A | ||

| 4 | n.c. | not connected | ||

| 5 | VGS(carr) | gate-source voltage of carrier [1] | ||

| 6 | VGS(peak) | gate-source voltage of peaking [2] | ||

| 7 | n.c. | not connected | ||

| 8 | VDS1_A | drain-source voltage of driver stages of section A | ||

| 9 | n.c. | not connected | ||

| 10 | c.t.g. | connect to ground | ||

| 11 | RF_IN_A | RF input of section A | ||

| 12 | GND | ground | ||

| 13 | GND | ground | ||

| 14 | RF_IN_B | RF input of section B | ||

| 15 | c.t.g. | connected to ground | ||

| 16 | n.c. | not connected | ||

| 17 | VDS1_B | drain-source voltage of driver stages of section B | ||

| 18 | n.c. | not connected | ||

| 19 | VGS(peak) | gate-source voltage of peaking [2] | ||

| 20 | VGS(carr) | gate-source voltage of carrier [1] | ||

| 21 | n.c. | not connected | ||

| 22 | decoupling_B | video-lead for decoupling of section B | ||

| 23 | n.c. | not connected | ||

| 24 | n.c. | not connected | ||

| 25, 26, 27 | RF_OUT_B/VDS2_B | RF output and drain-source voltage of final stages of section B | ||

| 28 | n.c. | not connected | ||

| 29 | GND | ground | ||

| 30 | GND | ground | ||

| 31 | n.c. | not connected | ||

| 32, 33, 34 | RF_OUT_A/VDS2_A | RF output and drain-source voltage of final stages of section A |

Documentation

| Title | Type | Date | |

|---|---|---|---|

| LDMOS 2-stage integrated Doherty MMIC | Data sheet | 2023-09-11 | |

| Mounting and soldering of RF transistors in overmolded plastic packages | Application note | 2025-02-03 | |

| Packages for RF power transistors | Leaflet | 2026-04-17 | |

| RF power solutions for Wireless Infrastructure | Brochure | 2026-04-20 |

Design support

| Title | Type | Date | |

|---|---|---|---|

| Printed-Circuit Board (PCB) B10H0710N40D (Data sheet) | Design support | 2023-10-02 |