Power LDMOS transistor

Based on Advanced Rugged Technology (ART), this 2000 W LDMOS RF power transistor has been designed to cover a wide range of applications for ISM, broadcast and communications. The unmatched transistor has a frequency range of 1 MHz to 450 MHz.

Features and benefits

- High breakdown voltage enables class E operation up to VDS = 53 V

- Qualified up to a maximum of VDS = 65 V

- Characterized from 30 V to 65 V to support a wide range of applications

- Integrated dual sided ESD protection enables class C operation and complete switch off of the transistor

- Excellent ruggedness with no device degradation

- High efficiency

- Excellent thermal stability

- Designed for broadband operation

- For RoHS compliance see the product details on the Ampleon website

Applications

- Industrial, scientific and medical applications

- Plasma generators

- MRI systems

- Particle accelerators

- Broadcast

- FM radio

- VHF TV

- Communications

- Non cellular communications

- UHF radar

Parametrics

| Symbol | Parameter | Conditions | Min | Typ/Nom | Max | Unit |

|---|---|---|---|---|---|---|

| frange | frequency range | 1 | 450 | MHz | ||

| PL(1dB) | nominal output power at 1 dB gain compression | 2000 | W | |||

| Test signal: Pulsed RF | ||||||

| VDS | drain-source voltage | PL = 2000 W [0] | 65 | V | ||

| Gp | power gain | PL = 2000 W [0] | 26.5 | 27.7 | dB | |

| RLin | input return loss | PL = 2000 W [0] | -15 | dB | ||

| ηD | drain efficiency | PL = 2000 W [0] | 68 | 71.7 | % | |

Package / Packing

| Type number |

Package type, (Package outline) |

Outline version | Packing | Product status | Marking |

Orderable part number, (Ordering code (12NC)) |

|---|---|---|---|---|---|---|

| ART2K0PE | OMP-1230 (OMP-1230-4F-1) |

omp-1230-4f-1_po | Tray; 20-fold; dry pack | Active | Standard Marking |

ART2K0PEZ (9349 606 96517) |

| TR13; 100-fold; 56 mm; dry pack | Active | Standard Marking |

ART2K0PEY (9349 606 96518) |

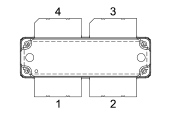

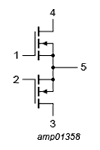

Pinning info

| Pin | Symbol | Description | Simplified outline | Graphic symbol |

|---|---|---|---|---|

| 1 | G1 | gate1 |

|

|

| 2 | G2 | gate2 | ||

| 3 | D2 | drain2 | ||

| 4 | D1 | drain1 | ||

| 5 | S | source [1] |

Documentation

Recommended line-up

Design support

| Title | Type | Date | |

|---|---|---|---|

| Printed-Circuit Board (PCB) ART2K0PE(G) (Data sheet) | Design support | 2023-09-15 | |

| ART2K0PE(G) Cauer Thermal Transient Impedance Model | Simulation model | 2023-09-15 | |

| ART2K0PE(G) Foster Thermal Transient Impedance Model | Simulation model | 2023-09-15 | |

| ART2K0PE SPICE Model | Simulation model | 2023-11-28 | |

| ART2K0PE 65 V 100 mA S-parameter data | S-parameter | 2023-09-15 | |

| ART2K0PE Model for ADS 2019 (Keysight Advanced Design System) | Simulation model | 2020-06-11 | |

| ART2K0PE Model for Cadence AWR Microwave Office® | Simulation model | 2023-09-15 | |

| ART2K0PE Simulation Example for Cadence AWR Microwave Office® | Simulation model | 2023-09-15 |