# AR211103 ART150PEG, 40MHz v1.0 - 02 April 2021

| Document information                                                                             |                   |  |  |  |

|--------------------------------------------------------------------------------------------------|-------------------|--|--|--|

| Status General Publication                                                                       |                   |  |  |  |

| Author(s)                                                                                        | Yevhen Tymofieiev |  |  |  |

| Abstract Measurement results of a class E generator design for the 40MHz band with the ART150PEG |                   |  |  |  |

## ART150PEG

40MHz

# 1. Revision History

| Revision | Date       | Description      | Author            |

|----------|------------|------------------|-------------------|

| 1.0      | 2021.04.02 | Initial document | Yevhen Tymofieiev |

## 2. Contents

| 1.  | Revision History           | 2    |

|-----|----------------------------|------|

| 2.  | Contents                   | 2    |

| 3.  | List of figures            | 2    |

| 4.  | List of tables             | 2    |

| 5.  | Description                | 3    |

| 5.1 | General description        |      |

| 5.2 | Theory of operation        |      |

| 5.3 | Design recommendations     | 4    |

| 6.  | Electrical characteristics | 5    |

| 6.1 | General characteristics    | 5    |

| 6.2 | Power sweep                | 6    |

| 7.  | Thermal characteristics    | 7    |

| 8.  | Hardware                   | 8    |

| 8.1 | Bill of materials          | 8    |

| 8.2 | Component mapping          | 9    |

| Boa | rd specifications          | . 10 |

| 8.3 | Demo markings              | . 10 |

| 9.  | Legal information          | . 11 |

| 9.1 | Definitions                | . 11 |

| 9.2 | Disclaimers                | . 11 |

| 9.3 | Trademarks                 |      |

| 9.4 | Contact information        | . 11 |

## 3. List of figures

| Figure 1 | Demo front view                                            | .3  |

|----------|------------------------------------------------------------|-----|

| Figure 2 | Schematic                                                  | . 4 |

| Figure 3 | Output power and efficiency as a function of drain voltage | . 6 |

| Figure 4 | IR picture                                                 | . 7 |

| Figure 5 | Component mapping                                          | .9  |

# 4. List of tables

| Table 1: |                                                            | 2  |

|----------|------------------------------------------------------------|----|

| Table 2: | Electrical characteristics                                 | 5  |

| Table 1: | Output power and efficiency as a function of drain voltage | 6  |

|          | Bill of Materials                                          |    |

| Table 3: | Board specifications                                       | 10 |

| Table 4: | Device specifics                                           | 10 |

ART150PEG

## 5. Description

#### 5.1 General description

This report presents the measurement results of the Class E generator demo AR211065. The device used is ART150PEG, Advanced Rugged Technology (ART) LDMOS power transistor. The presented demo is operating at 40MHz.

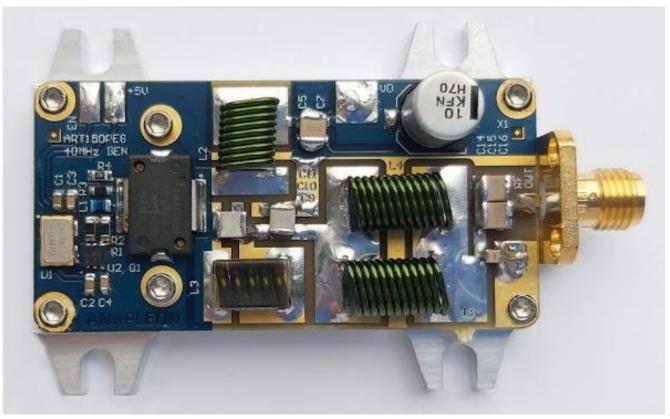

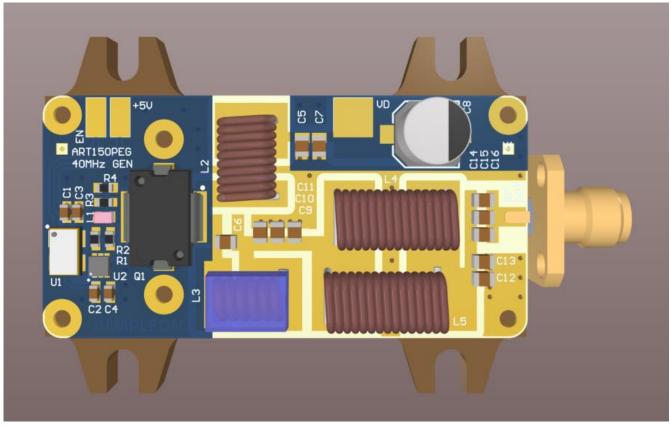

Figure 1 Demo front view

AR211065

AR211103

#### ART150PEG

#### 5.2 Theory of operation

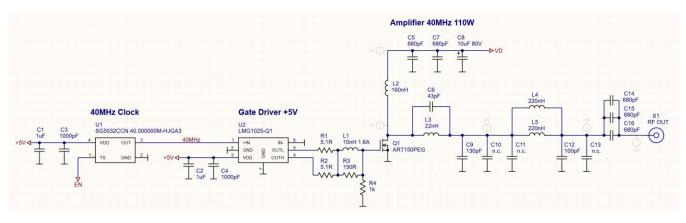

The demo lineup consists of a 40MHz clock U1, gate driver U2, pre-distortion network, LDMOS transistor Q1 and the output matching (*Figure 1*).

40MHz clock U1 is the crystal oscillator with digital CMOS output. It provides the signal to Schmitt trigger at the non-inverting input of the gate driver U2. The output stage of the driver U2 is connected to the gate of Q1 via current limiting resistors (R1, R2) and pre-distortion network (L1, R3). The predistortion network is boosting the rise and fall times of the pulse on the capacitive gate of Q1 and therefore reduces the losses in transistor Q1 during the switching between 0V and 5V. The output matching network provides a proper transformation ratio and helps to reduce the level of harmonics.

Output RF power at the connector X1 can be regulated with variable  $V_{DD}$  coming from the switching mode power supply (SMPS) in the range of 5 to 135W.

Figure 2 Schematic

#### 5.3 Design recommendations

The frequency of operation is set by the clock U1 and can be adjusted by the IC supplier on request. The output matching supports the 40-42MHz frequency range.

In class E amplifier, peak voltage on the physical drain of transistor can reach approximately 3.5 times  $V_{DD}$ . Long-term operation at  $V_{DD}$  > 55V is not recommended.

Because of the high impedance of the interface between U1 and U2, the line on PCB is kept as short as possible. Local SMD shield covering U1, U2 and all the peripheral components might help to reduce coupling from the output matching.

The pre-distortion network might create positive and negative voltage spikes outside of the safe operating region of the gate driver U2. It is important to dump those spikes using R1-R3.

The gate driver U2 could be driven directly from the microcontroller to enable output power adjustment via pulse-width modulation (PWM).

It is possible to run the demo in pulsed mode by applying the modulation/enable signal to pin1 of U1. When operating in this mode, it might be necessary to check the ripple current in capacitor C8.

1111 capacitors C5, C6, C7, C9, C12, C14, C15, C16 shown in *Figure 1* have been replaced with cheaper 0805 capacitors (shown in the bill of materials) without any significant change in electrical or thermal characteristics.

As explained in chapter 7, two inductors 2222SQ-221GE (L4, L5) connected in parallel can be replaced with one inductor 1010VS-111ME.

All information provided in this document is subject to legal disclaimers.

AR211065

## ART150PEG

40MHz

## 6. Electrical characteristics

#### 6.1 General characteristics

Table 2: Electrical characteristics

CW operation; 50R load; RF power measured after LPF; Tbaseplate =40°C

| Symbol                 | Parameter                             | Unit | Min  | Тур             | Max  |

|------------------------|---------------------------------------|------|------|-----------------|------|

| F                      | Frequency range of output matching    | MHz  | 40   | 40 <sup>1</sup> | 42   |

| V <sub>DD</sub>        | Drain voltage of LDMOS section        | V    | 10   | 50              | 55   |

| I <sub>DD</sub>        | Current consumption of LDMOS section  | А    | -    | 2.7             | -    |

| V <sub>DRIVER</sub>    | Voltage supply of driver section      | V    | 4.75 | 5               | 5.25 |

| IDRIVER                | Current consumption of driver section | mA   | -    | 73              | -    |

| Pout                   | Output power                          |      | 5.1  | 115             | 134  |

| $\eta_{\text{drain}}$  | Drain efficiency                      |      | -    | 86              | -    |

| $\eta_{\text{LINEUP}}$ | Lineup efficiency                     |      | -    | 85.5            | -    |

| PDISS                  | Dissipated power                      | W    | 1.8  | 19              | 25   |

| H <sub>2</sub>         | Level of 2 <sup>nd</sup> harmonic     | dBc  | -    | -18             | -    |

| H <sub>3</sub>         | Level of 3 <sup>rd</sup> Harmonic     |      | -    | -35             | -    |

<sup>1</sup> Frequency of operation is set by the clock U1

#### ART150PEG

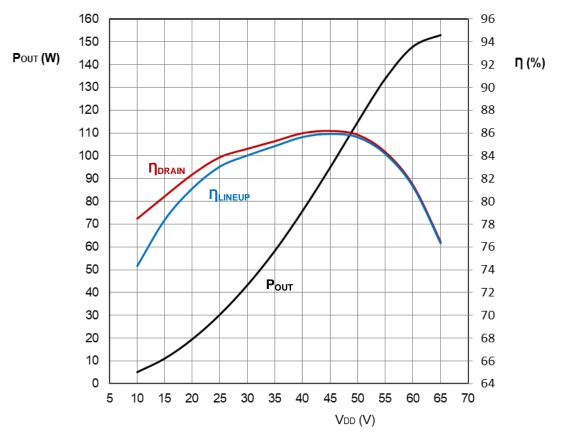

#### 6.2 Power sweep

Table 1:

Output power and efficiency as a function of drain voltage

CW operation; 50R load; RF power measured after LPF; Tbaseplate =40°C

| $V_{DD}, \vee$  | I <sub>DD</sub> , A | <b>Ρ</b> ουτ, W | <b>N</b> drain, % | <b>Ŋ</b> lineup, % | ₽ <sub>DISS</sub> ², W |

|-----------------|---------------------|-----------------|-------------------|--------------------|------------------------|

| 10              | 0.65                | 5.1             | 78.5              | 74.3               | 1.8                    |

| 15              | 0.92                | 11.1            | 80.4              | 78.4               | 2.7                    |

| 20              | 1.19                | 19.6            | 82.4              | 81.1               | 4.2                    |

| 25              | 1.45                | 30.4            | 83.9              | 83.0               | 5.9                    |

| 30              | 1.71                | 43.4            | 84.6              | 84.0               | 7.9                    |

| 35              | 1.96                | 58.5            | 85.3              | 84.8               | 10.1                   |

| 40              | 2.21                | 76              | 86.0              | 85.6               | 12.4                   |

| 45              | 2.45                | 95              | 86.2              | 85.9               | 15.3                   |

| 50              | 2.68                | 115             | 85.8              | 85.6               | 19.0                   |

| 55              | 2.89                | 134             | 84.3              | 84.1               | 25.0                   |

| 60 <sup>1</sup> | 3.03                | 148             | 81.4              | 81.2               | 33.8                   |

| 65 <sup>1</sup> | 3.08                | 153             | 76.4              | 76.3               | 47.2                   |

<sup>1</sup> Long-term operation at  $V_{DD}$  > 55V is not recommended

<sup>2</sup> Power dissipated in transistor Q1

All information provided in this document is subject to legal disclaimers. © Ampleon The Netherlands B.V. 2021. All rights reserved.

AR211065

AR211103

#### ART150PEG

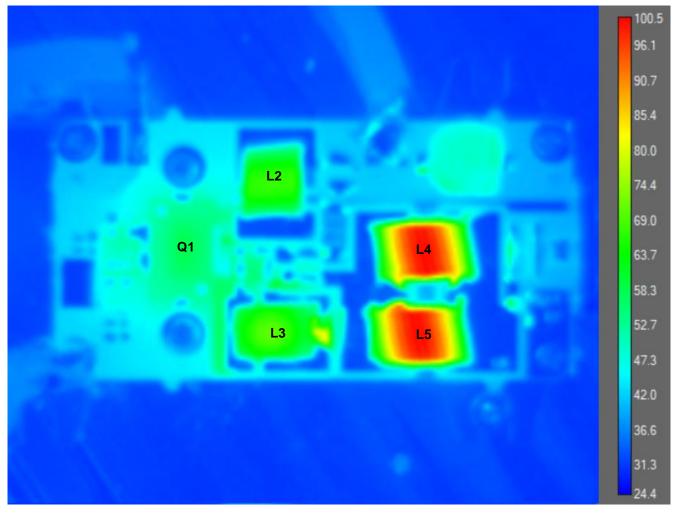

The board has been measured during RF operation with IR camera to detect hotspots.

Test conditions:

$V_{DD} = 50V;$

POUT = 110W CW, 50R load, RF power measured after LPF;

Tbaseplate =40°C

Figure 4 IR picture

The board has two hotspots – L4, L5. Both get a temperature rise of 60°C.

Those two 220nH 5A inductors 2222SQ-221GE connected in parallel were used in the demo design because of the tight  $\pm 2\%$  tolerance. It is possible to replace L4 and L5 just with one 111nH 22A inductor 1010VS-111ME. It is up to customer to decide if  $\pm 20\%$  tolerance of 1010VS-111ME can provide sufficient yield in mass production.

AR211103

ART150PEG

## 8. Hardware

## 8.1 Bill of materials

| Table 2: Bill of Materials |            |           |           |                               |                      |          |

|----------------------------|------------|-----------|-----------|-------------------------------|----------------------|----------|

| Designator                 | Group      | Value     | Tolerance | Name                          | Manufacturer         | Quantity |

| C1, C2                     | Capacitor  | 1uF       | ±10%      | 06036D106MAT4A                | AVX                  | 2        |

| C3, C4                     | Capacitor  | 1000pF    | ±5%       | 06035A102JAT2A                | AVX                  | 2        |

| C5, C7, C14,<br>C15, C16   | Capacitor  | 680pF     | ±5%       | VJ0805D681KXBAJ               | Vishay               | 5        |

| C6                         | Capacitor  | 43pF      | ±5%       | 08051U430JAT2A                | AVX                  | 1        |

| C8                         | Capacitor  | 10uF 80V  | ±20%      | EEE-FN1K100XL                 | Panasonic            | 1        |

| C9                         | Capacitor  | 130pF     | ±5%       | 08052U131JAT2A                | AVX                  | 1        |

| C12                        | Capacitor  | 100pF     | ±5%       | 08052U101JAT2A                | AVX                  | 1        |

| L1                         | Inductor   | 10nH 1.6A | ±2%       | LQW18AN10NG8ZD                | Murata               | 1        |

| L2                         | Inductor   | 160nH     | ±2%       | 2222SQ-161GE                  | Coilcraft            | 1        |

| L3                         | Inductor   | 22nH      | ±5%       | WA3097-AL                     | Coilcraft            | 1        |

| L4, L5                     | Inductor   | 220nH     | ±2%       | 2222SQ-221GE                  | Coilcraft            | 2        |

| Q1                         | Transistor |           |           | ART150PEG                     | Ampleon              | 1        |

| R1, R2                     | Resistor   | 5.1R      | ±5%       | ERJ-PA3J5R1V                  | Panasonic            | 2        |

| R3                         | Resistor   | 150R      | ±1%       | ERJ-PA3F1500V                 | Panasonic            | 1        |

| R4                         | Resistor   | 1k        | ±1%       | ERJ-PA3F1001V                 | Panasonic            | 1        |

| U1                         | IC         | 40MHz     |           | SG5032CCN<br>40.000000M-HJGA3 | Epson                | 1        |

| U2                         | IC         |           |           | LMG1025-Q1                    | Texas<br>Instruments | 1        |

40MHz

AR211103

8 of 11

### ART150PEG

AR211103

40MHz

### 8.2 Component mapping

Figure 5 Component mapping

### ART150PEG

AR211103 40MHz

### **Board specifications**

| Table 3: Board specifications                                                        |                                  |  |  |  |  |

|--------------------------------------------------------------------------------------|----------------------------------|--|--|--|--|

| Parameter                                                                            | Value                            |  |  |  |  |

| Manufacturer                                                                         | EMC                              |  |  |  |  |

| Туре                                                                                 | EM-827BI (Lead free FR4)         |  |  |  |  |

| Dk                                                                                   | 4.8 @ 1MHz<br>4.2 @ 1GHz         |  |  |  |  |

| Df                                                                                   | 0.018 @ 1MHz<br>0.019 @ 1GHz     |  |  |  |  |

| Laminate thickness                                                                   | 0.5mm / 1 oz.                    |  |  |  |  |

| Layers                                                                               | 2, top/bottom. Bottom all copper |  |  |  |  |

| Board specifics         Transistor Q1 is mounted on an I-shaped copper insert (coin) |                                  |  |  |  |  |

| Board dimensions     50 x 25mm                                                       |                                  |  |  |  |  |

## 8.3 Demo markings

| Table 4: Device specifics |                     |

|---------------------------|---------------------|

| Parameter                 | Value               |

| Manufacturer              | Ampleon             |

| Device                    | ART150PEG           |

| PCB marking               | ART150PEG 40MHz GEN |

ART150PEG

# 9. Legal information

### 9.1 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Ampleon does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

### 9.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, Ampleon does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. Ampleon takes no responsibility for the content in this document if provided by an information source outside of Ampleon.

In no event shall Ampleon be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, Ampleon's aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of Ampleon.

**Right to make changes** — Ampleon reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — Ampleon products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an Ampleon product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Ampleon and its suppliers accepts no liability for inclusion and/or use of Ampleon products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

### 9.4 Contact information

For more information, please visit: http://www.ampleon.com

For sales office addresses, please visit: http://www.ampleon.com/sales

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. Ampleon makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using Ampleon products, and Ampleon accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the Ampleon product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

Ampleon does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using Ampleon products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer's third party customer's. Ampleon does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

### 9.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

Any reference or use of any 'NXP' trademark in this document or in or on the surface of Ampleon products does not result in any claim, liability or entitlement vis-à-vis the owner of this trademark. Ampleon is no longer part of the NXP group of companies and any reference to or use of the 'NXP' trademarks will be replaced by reference to or use of Ampleon's own trademarks.

# AR211065